Digital Sensor IP

Universal fully-integrated fault attack sensor

In cryptography, an attack can be performed by injecting one or several faults into a device thus disrupting the functional behavior of the device. Techniques commonly used to inject faults consist in introducing variations in the source voltage, clock frequency, temperature, or irradiating with a laser beam etc.

Unlike analog sensors that are dedicated to detecting a specific perturbation attack, the Digital Sensor is designed to detect various threats belonging to the Fault Injection Attacks (FIA) family including:

- Input clock frequency (clock glitches, overclocking): reduction of the clock period to provoke a critical path violation;

- Input voltage (power glitches, underfeeding): reduction of the supply voltage to increase the propagation time of combinational logic;

- Temperature (heating): modification of the temperature to increase the propagation time;

- Radiations (laser spot, light spot, electromagnetic): cause the bit set or reset in the registers by irradiation.

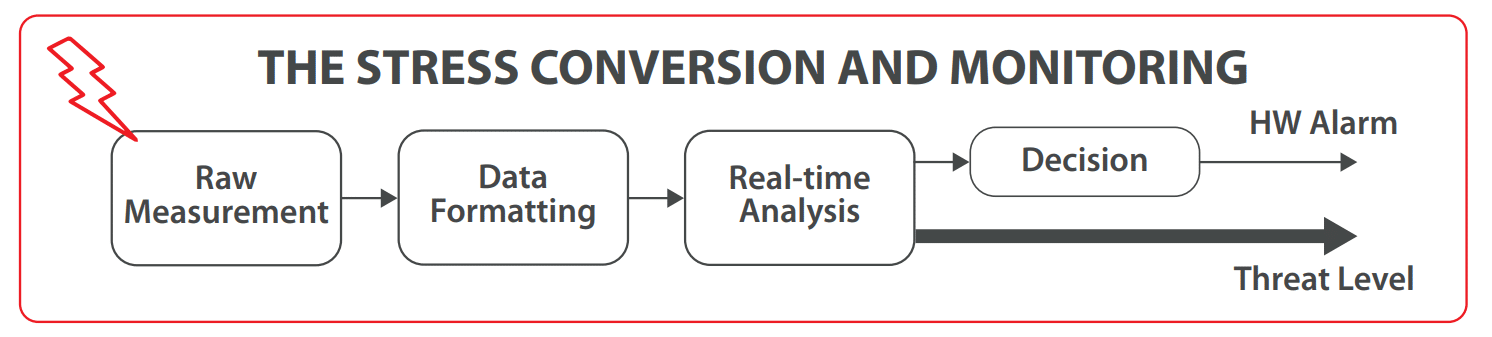

Digital Sensor converts all monitored stresses into a timing stress which is then measured. When a threat is detected, it provides the system with a measurement of the threat level and triggers the hardware alarm.

Digital Sensor IP acts as a Fault Injection Detection IP and offers the following features

Digital Sensor IP is a proven technology with stochastic model for reliability and security estimation that enables the detection of global and local fault injections as laser, EMFI (ElectroMagnetic Fault Injection), clock or temperature. It is difficult to identify by an attacker as it is blended into the rest of design.

- Real-time hardware alarm

- Embeds health-test to validate the integrity of the IP during the boot and on-demand

- Security certification ready (including Common Criteria)

- Fully digital and designed with a standard cells library

- Transferable to any design kit

- Lightweight

- Customizable sensitivity

- Compatible with clock gating feature

- Several sensors can be gathered around a single bus interface

- No calibration after design

- Support DVFS (Dynamic voltage and frequency scaling)

- Easy to integrate into the system

- Detect global and local Fault injections such as laser, EMFI, clock or temperature

- Diffi cult to identify by an attacker (melted within the rest of design)

- Proven technology with stochastic model for reliability and security estimation

- Tested in the Security Science Factory Lab, using global stress (e.g., clock glitch) and local stress (e.g., electromagnetic injection)

Digital Sensor IP has been tested in the Security Science Factory Laboratory, using global stress (e.g., clock glitch) and local stress (e.g., electromagnetic EM injection) to assess its robustness.